欢迎浏览厦门控匠自动化科技有限公司

行业资讯

MOTOROLA CPCI-6020 CompactPCI单板计算机

时间: 2026-02-09浏览次数:

MOTOROLA CPCI-6020 CompactPCI单板计算机

MOTOROLA CPCI-6020 CompactPCI单板计算机

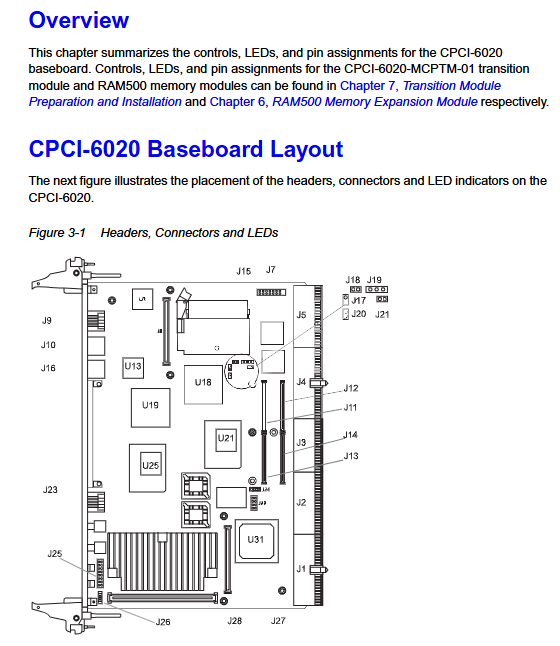

MOTOROLA CPCI-6020 系列 CompactPCI 单板计算机用户指南,面向系统集成、硬件配置及嵌入式开发人员,需具备 PCI 总线与 PowerPC 架构基础。手册核心介绍了该单板机以500MHz MPC7410 处理器为核心的硬件配置,涵盖 2MB L2 缓存、32MB 板载 Flash+1MB 插槽式 Flash、128MB-2GB ECC SDRAM(通过 RAM500 扩展模块),以及双 10BaseT/100BaseTx 以太网、双异步串口、USB、EIDE 等 I/O 接口;详细阐述了硬件拆包、跳线配置、模块(PMC/CompactFlash/RAM500)安装的实操步骤,定义了本地 PCI 总线 / VMEbus 的内存映射规则,解析了双 Harrier ASIC 控制器、ECC 内存、热插拔等核心功能的工作原理,同时明确了安全操作规范、EMI 合规要求及环境电源需求,配套 PPCBug 调试固件与诊断工具,是该单板机硬件部署、功能开发与故障排查的完整参考。

核心硬件规格

CPCI-6020 为 6U Eurocard 规格单板机,分 4 款型号(CPCI-60206E-500/505、CPCI-6020-500/505),核心差异为是否带 USB 和 Super I/O,核心硬件规格如下表:

表格

硬件类别 核心配置 关键参数 / 备注

处理器 MPC7410 500MHz,PowerPC 架构,带 Alti-Vec 技术,32 位数据 / 地址总线,支持奇偶校验

L2 缓存 后端缓存 2MB,流水线突发模式 SRAM,支持数据总线奇偶校验

闪存(Flash) 双 Bank 设计 Bank A:32MB 板载(1 颗 256Mbit 器件);Bank B:1MB 插槽式(2 颗 512Kbit 器件)

内存(SDRAM) ECC SDRAM 需 RAM500 扩展模块,单模块支持 128MB/256MB/512MB,双站点最大 2GB;支持单 bit 纠错 / 双 bit 检错

非易失存储 NVRAM/RTC/WDT M48T37V 提供 32KB NVRAM、RTC 时钟、看门狗;RTC 支持秒 / 分 / 时 / 日 / 月 / 年,BCD 格式

计时 / 看门狗 多模块协同 双 Harrier ASIC:各含 2 个 32 位可编程定时器 + 2 个独立看门狗;M48T37V:1 个可编程定时器

电源要求 多电压供电 +3.3V:2.6A 典型 / 3.5A 最大;+5V:2.8A 典型 / 3.75A 最大;±12V:各 100mA 最大;电压容差 ±5%

物理尺寸 6U Eurocard 符合 CompactPCI 规范,适配标准 CPCI 机箱导轨

工作环境 温 / 湿度 / 气流 工作温度:0-55℃(强制风冷);存储温度:-40-70℃;相对湿度:5%-90%(非凝露);最小气流:250 LFM(55℃环境)

硬件配置与安装

本章节详细说明 CPCI-6020 的拆包、跳线配置、模块安装步骤,核心操作均需在断电状态下进行,避免静电损坏电路,核心内容包括:

拆包要求:若包装箱损坏,需承运商代理在场拆包检验,保留包装材料用于存储 / 运输,操作前需确保工作环境符合 ESD 防护要求;

跳线配置:板卡含多个可配置跳线帽,为出厂默认配置,可根据需求修改,核心跳线功能如下表:

| 跳线编号 | 功能 | 出厂配置 | 可选配置 |

| J24 | Flash Bank 选择 | 2-3 短接(Bank B 启用,含 PPCBug) | 1-2 短接(Bank A 启用,32MB) |

| J22 | Harrier 上电配置 | 全断开(PUST0-3=1) | 1-2 短接(PUST0=0)、3-4 短接(PUST1=0)等 |

| J21 | PMC 66MHz 禁用 | 断开(支持 66MHz) | 1-2 短接(强制 33MHz,避免禁用二级以太网) |

| J18 | ±12V 启用 / 禁用 | 断开(启用 ±12V) | 1-2 短接(禁用 ±12V,影响部分外设) |

| J17 | Bank A Flash 块锁定 | 断开(未锁定) | 1-2 短接(锁定 1 个以上 Flash 块,无法解锁) |

| J20 | Bank A Flash 写保护 | 断开(可写) | 1-2 短接(全 Flash 写保护) |

| J19 | 远程开关接口 | 无跳线 | 连接远程 Reset/Abort 开关,功能与前端面板一致 |

模块安装

RAM500 内存模块:每个站点最多安装 2 个(底部 + 顶部堆叠),需通过 140-pin 连接器与主板对接,安装时需对齐定位孔并紧固螺丝;

PMC 模块:安装于主板顶部,通过 J11-J14 连接器对接,支持 32/64 位 PCI 接口,需移除前端面板挡板并固定 4 颗螺丝;

CompactFlash 卡:插入 J15 连接器,需确保 Pin 1 对齐,安装前需关闭系统电源;

过渡模块(CPCI-6020-MCPTM-01):安装于机箱后部,通过 J3/J5 接口与主板通信,支持 PIM/SIM 模块扩展;

系统配套要求:完成 CPCI-6020 系统搭建,需配套CompactPCI 合规机箱、系统控制台终端、操作系统、CPCI-6020-MCPTM-01 过渡模块及连接线缆;

热插拔注意事项:支持外设板热插拔,系统槽热插拔需 HA 架构支持;非热插拔机箱需断电后安装 / 移除模块,避免数据丢失或硬件损坏。

操作指令

本章节核心介绍 CPCI-6020 的前端面板操作、内存映射规则、软件初始化及复位操作,是设备使用和程序开发的核心依据:

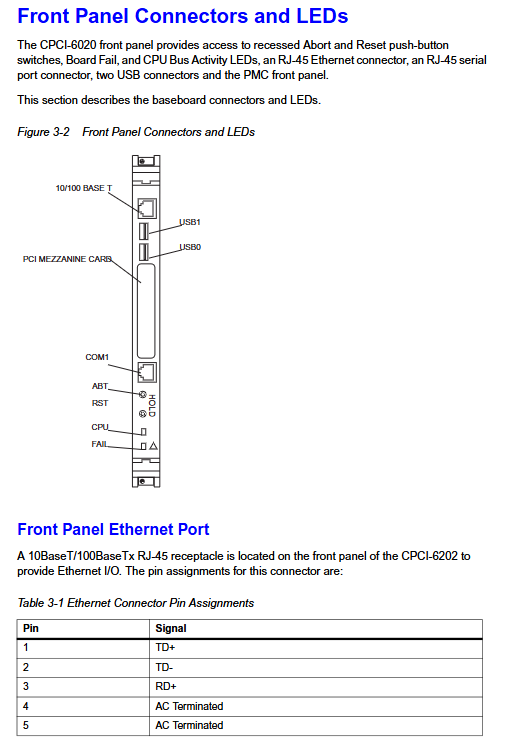

前端面板控件

按键:ABORT#( recessed 设计,避免误触,触发 MPIC 内部中断)、RESET#( recessed 设计,触发板级复位,信号经 Harrier ASIC 去抖);

2 个 LED 指示灯:CPU(绿色,处理器总线活跃时点亮)、BDFL(黄色,BDFL 总线活跃时点亮,软件可控);

内存映射:分本地 PCI 总线映射和CompactPCI 总线映射两类,本地 PCI 总线含 A/B 双总线,Bus A 支持 33MHz 固定速率,对接以太网、USB、EIDE 等外设;Bus B 支持 33/66MHz 切换,对接 PMC 插槽和二级以太网;CompactPCI 总线支持 A16/A24/A32 地址、D8/D16/D32 数据,通过 J1/J2 连接器与背板通信;

寄存器映射:核心寄存器区包括 Harrier ASIC 的 XCSR(配置状态寄存器)、MPIC(多处理器中断控制器)、EIDE 控制器、USB 控制器等,手册详细定义了各寄存器的地址、位宽、功能及默认值;

软件初始化:PPCBug 固件在上电 / 复位时完成处理器、内存、PCI 设备的初始化,默认配置无需修改即可启动操作系统;支持通过 CNFG 命令修改板卡信息(如序列号、总线时钟),通过 ENV 命令调整固件参数(如自动启动延时、内存大小限制);

复位操作

复位源:电源上电复位、前端面板 RESET# 按键、看门狗超时、软件硬复位(Harrier RSTOUT 位 / PBC Port 92)、CompactPCI PRST# 信号等;

影响范围:不同复位源影响设备不同,软件硬复位影响处理器、Harrier ASIC、PCI 设备等,CompactPCI 复位仅影响本地 CompactPCI 总线。

功能模块解析

本章节从硬件架构角度,解析 CPCI-6020 各核心模块的工作原理、接口规范、时序性能,核心内容包括:

核心总线架构:基于 PowerPlus III 架构,采用双 Harrier ASIC 作为系统内存控制器 / PCI 主机桥,实现处理器总线与 PCI 总线的桥接;Intel 21154 PCI-to-PCI 桥芯片提供本地 CompactPCI 总线扩展,支持 7 个外设槽;总线仲裁优先级:处理器 > Harrier ASIC > 外部 PCI 主设备;

核心存储模块

Flash:Bank A(32MB)为板载 16 位 Flash,Bank B(1MB)为插槽式 16 位 Flash,通过 J24 跳线选择复位向量源;Bank B 含 PPCBug 调试固件,重编程可能导致固件丢失;

SDRAM:由 RAM500 扩展模块提供,支持 ECC 校验(72 位宽,含 8 位校验位),每个 RAM500 模块含 9 颗 SDRAM 芯片(x8 配置)和 1 颗 SPD Serial EEPROM,通过 I2C 总线上报内存配置;

NVRAM/RTC:M48T37V 器件提供 32KB 非易失存储和 RTC 功能,电池备份确保断电后数据不丢失;

通信与扩展接口

以太网:双 10BaseT/100BaseTx 接口(Intel 82551IT),Primary 端口默认前置(RJ-45),Secondary 端口后置(通过过渡模块);支持 Auto-MDI/MDI-X,符合 IEEE 802.3 标准;

串口:2 个 16550 兼容异步串口(Harrier UART0/UART1),1 个前置(RJ-45,DCE 配置),1 个后置(通过过渡模块);2 个同步 / 异步串口(Z85230 ESCC),需通过 SIM 模块扩展为 EIA-232-D 标准;

USB:2 个 USB 2.0 端口(前置,Series A 接口),支持高速 / 全速 / 低速设备,由 NEC uPD720101 控制器驱动,支持控制 / 中断 / 批量 / 等时传输;

PMC 插槽:1 个 32/64 位 PMC 插槽(J11-J14),支持 33/66MHz 速率,支持 PIM 模块扩展 I/O 功能,PMC 用户 I/O 信号通过 J3/J5 连接器路由至过渡模块;

EIDE 接口:支持 Primary(对接 CompactFlash)和 Secondary(对接外部设备)通道,支持 PIO 加速传输和 DMA 模式,符合 ATAPI 标准;

本地资源

定时器 / 看门狗:双 Harrier ASIC 各含 2 个 32 位可编程定时器(1μs 分辨率)和 2 个独立看门狗(超时可触发复位或中断);M48T37V 含 1 个可编程定时器,超时触发硬复位;

I2C 总线:支持 2 路 I2C 主接口,对接 Serial EEPROM(VPD 存储)、SPD 内存配置芯片等,通信速率可编程;

中断控制器:MPIC(多处理器中断控制器)支持 8 个可编程硬件中断,支持电平 / 边沿触发,中断优先级可配置;

高可用(HA)特性:支持系统槽热插拔(需 HA 机箱),通过 BD_SEL#、HEALTHY# 信号实现热插拔检测;支持总线冗余仲裁和双 Harrier 协同工作,确保系统稳定运行。

安全与合规

安全操作规范:设备存在致命高压,操作时需接地、使用 ESD 防护装备、禁易爆环境、禁私自拆卸盖板(仅授权人员可拆机)、禁单人维修、热插拔前需关闭软件;

EMI 合规:为 A 级数字设备,需在合规机箱中使用,核心要求为外部 I/O 端口用屏蔽线、线缆屏蔽层接地、机箱导轨接地、拧紧面板螺丝,否则可能导致射频发射超标;

冷却需求:55℃环境下需 250 LFM 强制风冷,CPU 为主要热源,需确保散热通道畅通;避免高功耗模块相邻安装,高温环境需增加气流;

数据安全:Flash 重编程前需备份固件,避免覆盖 PPCBug;热插拔模块前需关闭操作系统和应用程序,防止数据损坏或文件系统崩溃;

环境合规:符合 RoHS 6/6 标准,禁用铅、汞等有害物质;废弃模块需按当地法规处理。

配套资源

固件:PPCBug 调试固件(含调试和诊断功能),支持内存读写、断点调试、汇编 / 反汇编、自检测试等;提供丰富命令集(如 MD 内存显示、GO 执行程序、HE 帮助),支持 CNFG/ENV 命令配置系统参数;

软件:支持 VMEexec 驱动包、USB 2.0 驱动、EIDE 驱动、Floppy 控制器驱动等;兼容第三方 PowerPC 架构应用程序,可通过摩托罗拉销售处获取;

相关文档:配套 MPC7410 用户手册、Harrier ASIC 编程指南、PPCBug 固件用户手册、RAM500 模块手册、CPCI-6020 编程参考指南等,以及 CompactPCI、PCI、ISA 等行业标准文档;

技术支持:可通过摩托罗拉销售处获取 CPCI-6020 的连接器信号定义、零件清单、原理图,免费提供;支持 RISCWatch 调试接口和 Mictor 调试连接器,便于硬件调试。