欢迎浏览厦门控匠自动化科技有限公司

行业资讯

MOTOROLA MVME162嵌入式控制器

时间: 2026-02-09浏览次数:

MOTOROLA MVME162嵌入式控制器

MOTOROLA MVME162嵌入式控制器

摩托罗拉推出的MVME162 系列嵌入式控制器(001 至 043 型号)的用户指南,发布于 1994 年,面向 OEM 系统设计、系统拓展及实验室实验人群,需使用者具备计算机和数字逻辑基础。手册核心介绍了该控制器以25MHz MC68LC040/MC68040 为核心的硬件配置,涵盖 1/4/8MB DRAM、512KB 带电池备份的 SRAM、1MB Flash 内存等核心存储,以及双串口、可选 SCSI/Ethernet/VMEbus/4 个 IndustryPack 接口等 I/O 功能;详细阐述了硬件拆包、跳线配置、模块安装的实操步骤,定义了本地总线 / VMEbus 的内存映射规则(含各类寄存器地址与功能),解析了控制器各核心模块的工作原理与时序性能,同时明确了安全操作规范、FCC 合规要求、冷却需求及串口互连的 EIA-232-D/EIA-530 标准,还配套了 162Bug 调试固件等软件资源,是该控制器硬件操作、功能开发与故障排查的完整参考。

核心硬件规格

MVME162 为双高 VME 模块,分 21 款型号(001-043),核心配置围绕25MHz 32 位 MC68LC040/MC68040 处理器展开,两款处理器均含 8KB 缓存 + MMU,MC68040 额外带浮点协处理器(FPU),各型号核心差异为 DRAM 容量、是否带 SCSI/Ethernet/VMEbus 接口,核心硬件规格如下表:

表格

硬件类别 核心配置 关键参数 / 备注

处理器 MC68LC040/MC68040 25MHz,32 位,前者无 FPU,后者带 FPU

主存储 DRAM 1/4/8MB 可选,带可编程奇偶校验,1MB 为非交错架构,4/8MB 为交错架构

静态存储 SRAM 512KB,带电池备份,最坏情况备份 200 天,无奇偶校验

只读 / 闪存 EPROM+Flash 4Mbit EPROM 插槽(JEDEC 32 针 PLCC);1MB Flash(旧板 1 颗 28F008SA,新板 4 颗 28F020)

非易失存储 NVRAM+TOD 时钟 Thompson MK48T08,8K×8 NVRAM,带电池备份,TOD 时钟支持秒 / 分 / 时 / 日 / 月 / 年,BCD24 小时制

计时 / 看门狗 MCchip+VMEchip2 MCchip:4 个 32 位可编程定时器(1μs 分辨率)+1 个看门狗;VMEchip2:2 个 32 位可编程定时器 + 1 个看门狗

电源要求 直流供电 +5V (±5%):3.5A 典型,4.5A 最大;+12Vdc (±5%):100mA 最大;-12Vdc (±5%):100mA 最大

物理尺寸 双高 VME 板 仅板卡:233mm×160mm×17mm;带连接器 / 面板:262mm×188mm×20.32mm

工作环境 温 / 湿度 工作温度:0-70℃(强制风冷出口温度);存储温度:-40-85℃;相对湿度:5%-90%(非凝露)

硬件配置与安装

本章节详细说明 MVME162 的拆包、跳线配置、模块安装步骤,核心操作均需在断电状态下进行,避免静电损坏电路,核心内容包括:

拆包要求:若包装箱损坏,需承运商代理在场拆包检验,保留包装材料用于存储 / 运输,避免触摸集成电路区域;

跳线配置:板卡含多个可配置跳线帽,为出厂默认配置,可根据需求修改,核心跳线功能如下表:

| 跳线编号 | 功能 | 出厂配置 | 可选配置 |

| J1 | 系统控制器选择 | 1-2 短接(为 VMEbus 系统控制器) | 移除跳线(非系统控制器) |

| J11 | 串口 1 / 控制台时钟 | 无跳线(异步通信) | 1-2、3-4 短接(同步外部时钟) |

| J12 | 串口 2 时钟 | 无跳线(异步通信) | 1-2、3-4 短接(同步外部时钟) |

| J20 | SRAM 备份电源 | 1-3、2-4 短接(VMEbus +5V 备用电源) | 3-5、4-6 短接(板载电池) |

| J21 | EPROM 容量选择 | 2-3 短接(4Mbit,唯一可用规格) | - |

| J22 | 通用可读跳线 | 全短接(全 0) | 部分移除,对应寄存器值为 1,GPIO3(9-10)用于选择 Flash/EPROM |

SIM 串口模块:串口 2(Port B)通过 J10 接口搭载 SIM 模块,支持 EIA-232-D/EIA-530 的 DTE/DCE 四种类型,模块可插拔更换,核心型号为 SIM05-SIM08;

模块安装

IP 模块:最多安装 4 个,分别对应 J2/J3、J7/J8、J13/J14、J18/J19 接口,支持双尺寸 IP 模块;

MVME162 板卡:若为系统控制器,需安装在 VME 机箱最左侧插槽 1,需拆除插槽的 IACK/BG 跳线,与 P1/P2 背板连接器牢固连接;

过渡模块:需配套 MVME712 系列过渡模块,仅可使用其串口 2/4,禁止使用 1/3 和打印机口,EIA-530 配置时不可用该模块;

系统配套要求:完成 MVME162 系统搭建,需配套系统控制台终端、磁盘驱动器及控制器、操作系统、MVME712 过渡模块 + P2/LCP2 适配器板及线缆。

操作指令

本章节核心介绍 MVME162 的前端面板操作、内存映射规则、软件初始化及复位操作,是设备使用和程序开发的核心依据:

前端面板控件

按键:ABORT (S1)(软件使能后产生可编程中断,返回 162Bug)、RESET (S2)(复位板上所有设备,若为系统控制器则驱动 SYSRESET*);

8 个 LED 指示灯:FAIL(红,BRDFAIL * 激活)、STAT(黄,处理器暂停)、RUN(绿,本地总线周期执行)、SCON(绿,为 VMEbus 系统控制器)、LAN(绿,LAN 芯片为本地总线主设备)、FUSE(绿,LAN 收发器电源正常)、SCSI(绿,SCSI 芯片为本地总线主设备)、VME(绿,使用 VMEbus);

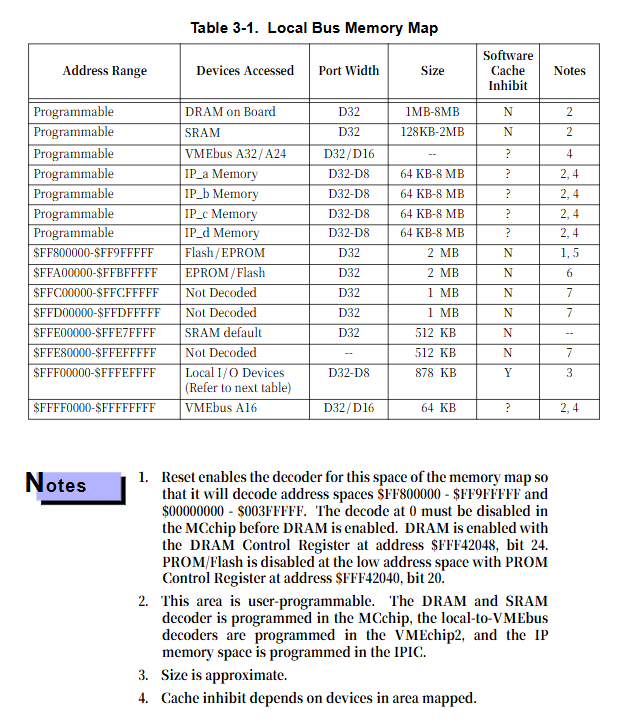

内存映射:分本地总线内存映射和VMEbus 内存映射两类,本地总线地址范围为

00000000−

FFFFFFFF,核心划分包括可编程 DRAM/SRAM/IP 内存区、

FF800000−

FF9FFFFF 的 Flash/EPROM 区、

FFF00000−

FFFEFFFF 的本地 I/O 设备区(含各类寄存器)、

FFFF0000−

FFFFFFFF 的 VMEbus A16 区;本地 I/O 设备区包含 VMEchip2、MCchip、SCC、LAN、SCSI、IPIC、TOD 时钟等核心寄存器,手册详细定义了各寄存器的地址、位宽、功能;

BBRAM/TOD 时钟映射:MK48T08 的 8KB NVRAM 分为用户区、网络区、系统区、调试区、配置区(256B)、TOD 时钟区(8B),配置区存储板卡序列号、Ethernet 地址、SCSI ID 等关键信息,末尾 1 字节为校验和;

软件初始化:162Bug 调试固件在上电 / 复位时完成大部分控制寄存器的默认配置,若需自定义配置,需参考 M68040 手册和 MVME162 编程参考指南;多 MPU 系统中,同一时间仅允许一个 MPU 控制寄存器,避免冲突;

复位操作

系统复位(SYSRESET*):由复位键、上电、看门狗超时、VMEchip2 LCSR 位触发,持续至少 200ms,符合 VMEbus 规范;

本地复位(LRST):为系统复位子集,5 种触发方式(看门狗超时、复位键、GCSR 位、SYSRESET*、上电),VMEbus 主设备可通过 GCSR 复位本地总线,该操作存在风险,仅在设备故障时使用。

功能模块解析

本章节从硬件架构角度,解析 MVME162 各核心模块的工作原理、接口规范、时序性能,核心内容包括:

本地总线架构:32 位同步总线,基于 MC68040 总线,支持突发传输和侦听,总线仲裁为优先级仲裁,主设备优先级从高到低为LAN(82596CA) > SCSI(53C710) > VMEbus > MPU;

核心存储模块

DRAM:由 MCchip 控制,基地址、容量可编程,奇偶校验错误可触发中断 / 总线异常,需至少 10 个初始化周期;

SRAM:512KB 32 位,由 Dallas DS1210S 实现电池备份,支持 VMEbus +5V 备用电源和板载电池双备份,板载电池为 RAYOVAC FB1225(两颗 BR1225 锂电池),40℃断电状态下至少备份 2 年;

Flash/EPROM:由 MCchip 实现 8 位到 32 位的总线转换,通过 J22 的 GPIO3 选择复位代码读取源(Flash/EPROM);

通信与扩展接口

双串口:由 Zilog Z85230 控制,串口 1 为 EIA-232-D DCE,串口 2 可选 EIA-232-D/EIA-530 的 DTE/DCE,支持异步(110B/s-38.4KB/s)和同步(SDLC/HDLC)协议,支持 CTS/DCD/RTS/DTR 控制信号;

Ethernet:由 Intel 82596CA 控制,带 32 位本地总线 DMA,板卡唯一 Ethernet 地址为 $08003E2xxxxx,存储在 BBRAM 和板卡标签上,LAN DMA 不可访问 VMEbus,避免缓冲区溢出;

SCSI:由 NCR 53C710 控制,带 32 位本地总线突发 DMA,支持 SCSI 总线,总线两端需正确端接,适配器板提供端接电阻插槽和熔丝;

IndustryPack:由 IPIC ASIC 控制,支持 4 个 IP 接口,接口为 3M 连接器,内存 / I/O 空间可编程,支持中断控制;

VMEbus:由 VMEchip2 ASIC 实现,为工厂可选配置,不支持现场加装,支持 A24/A32 地址、D8/D16/D32 数据,支持 DMA 突发传输(D64/MBLT),提供系统控制器、中断处理、总线仲裁等功能;

本地资源

可编程定时器:MCchip4 个 + VMEchip22 个,32 位,1μs 分辨率,可生成周期性中断;

看门狗定时器:MCchip 和 VMEchip2 各 1 个,独立工作,超时可触发 SYSRESET*、本地复位、板卡故障信号;

硬件中断:VMEchip2 提供 8 个软件可编程硬件中断,可由软件触发硬件中断;

本地总线超时:VMEchip2 和 MCchip 均提供超时功能,超时值可选 8/64/256μs / 无限,超时后向主设备发送 TEA 信号,无 VMEbus 的板卡由 MCchip 实现该功能;

时序性能:核心为 DRAM 读写周期,25MHz 下非交错 DRAM 读周期为 4,2,2,2,交错 DRAM 读周期为 4,1,1,1,写周期为 3,2,2,2;EPROM/Flash 周期为 3-10 总线时钟 / 字节,可编程配置;SCSI DMA 传输速率为 44MB/s(25MHz,无校验,交错 DRAM),LAN DMA 传输速率为 20MB/s(25MHz,无校验)。

串口互连规范

本章节详细定义了 MVME162 双串口的互连标准,支持EIA-232-D和EIA-530两种规范,核心内容包括:

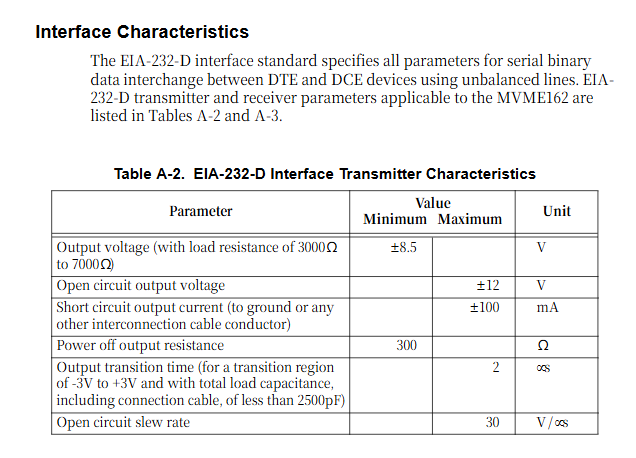

EIA-232-D:单端信号,DB25 接口,定义了 25 个引脚的信号功能,核心使用 TxD/RxD/RTS/CTS/DSR/DCD/DTR/SG,适用于短距离传输(建议≤15m),总负载电容≤2500pF,手册定义了发射器 / 接收器的电气特性(输出电压 ±8.5V 最小,输入阈值 ±2.25V/±0.75V);

EIA-530:支持平衡 / 单端信号,DB25 接口,为 EIA-232-D 的升级,支持更高传输速率,核心信号为差分信号(如 TxD_A/TxD_B),手册定义了发射器 / 接收器的电气特性(差分输出电压≥2.0V,输入阈值 ±200mV);

接地要求:信号地(Pin7)必连,完成电路回路;机箱地(Pin1)慎用,避免不同设备地电位差导致的电流和数据干扰,仅在一处将信号地与机箱地连接(建议在计算机端)。